Un flip-flop di tipo D preso ad esempio per introdurre i 4 possibili modi di rappresentare i diagrammi temporali così come ce li introduce Alan Clements nel suo Microprocessor System Design.

La scelta è ricaduta su questo dispositivo, come lo stesso Clements ci dice, in quanto rappresenta un elemento di memoria base e si comporta nella cattura dei dati proprio come un microprocessore.

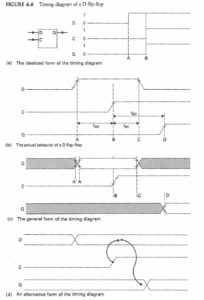

La figura 4.6a rappresenta il comportamento ideale del flip-flop.

I cambiamenti di stato sono istantanei.

Nella figura 4.6b è mostrato il comportamento reale del dispositivo.

Ora non abbiamo più a che fare con fronti di salita verticali ma siamo di fronte a linee inclinate.

Ovviamente i nuovi fronti di salita non sono rappresentati in scala e quindi non forniscono indicazioni precise sui tempi impiegati per l’effettivo cambio di stato.

Possiamo semplicemente affermare che la variazione dello stato logico sarà avvenuta quando la tensione avrà superato la soglia di commutazione del dispositivo.

Così vengono introdotti i seguenti livelli di riferimento:

- Vol : Il voltaggio massimo in uscita da un dispositivo allo stato logico 0.

- Voh : Il voltaggio minimo in uscita da un dispositivo allo stato logico 1.

- Vil : Il voltaggio massimo in ingresso ad un dispositivo affinchè questo interpreti il segnale come allo stato logico 0.

- Vih : Il voltaggio minimo in ingresso ad un dispositivo affinché questo interpreti il segnale come allo stato logico 1.

Sempre osservando la figura 4.6b definiamo Tab come il tempo intercorso tra il raggiungimento del livello logico 1 (Vih) da parte dell’ingresso D ed il fronte di salita di C (segnale di clock).

Chiameremo questo lasso di tempo setup time.

Setup time rappresenta il tempo minimo per il quale i dati devono essere stabili all’ingresso della periferica (i.e. flip-flop) prima che possano essere ritenuti validi. (In questo caso ci riferiamo al fronte di salita del segnale C).

Parimenti definiremo Tbc come tempo di hold time.

Hold time è il tempo minimo per il quale i dati devono rimanere stabili dopo il segnale di fetch. (Come prima ci stiamo riferendo all’evento scatenato da C).

Non ultimo definiremo Tbd come il tempo massimo che potremo aspettarci affinché si possa ritenere valido l’output del dispositivo (segnale Q) in seguito all’impulso di clock (C).

Vogliamo ricordare il fatto che ogni violazione dei tempi di setup e/o di hold comportano trasferimenti di dati non attendibili.

Riassumendo e semplificando diciamo semplicemente che esiste un istante in cui i dati presenti sul bus vengono acquisiti dal richiedente.

Tale istante deve essere preceduto da un certo lasso di tempo (setup time) e seguito da un omologo lasso di tempo dopo il segnale di acquisizione (hold time).

Nella figura 4.6c è rappresentata la forma più comune di diagrammi temporali.

D e Q sono rappresentati come aree ombreggiate fino ai punti A e D rispettivamente.

Questo sta a significare che in questo lasso di tempo non siamo interessati al valore di questi 2 segnali.

Intendiamo infatti concentrarci esclusivamente al punto in cui avvengono i cambiamenti di stato.

Così vediamo che al punto A’ inizia il cambiamento di stato della linea D che sarà completo al punto A (istante dal quale inizieremo a misurare il tempo di setup).

Allo stesso modo non saremo interessati a ciò che accade dopo il punto C che è l’istante in cui termina il tempo di hold.

Come si evinceva anche dalla figura 4.6b il tempo che intercorre tra i punti A e C è quello in cui il segnale deve rimanere stabile. (Setup-time + hold-time).

La figura 4.6d enfatizza invece la relazione di causa/effetto tra gli eventi.

L’evento scatenante è il fronte di salita di C che causa il campionamento del segnale D che verrà a sua volta trasferito all’uscita Q.

Per il momento è tutto!