MC68000 cicli di bus sincroni ed asincroni, accessi in scrittura e lettura

Continuiamo questa serie di articoli con la descrizione dei cicli di bus, i.e. accessi alla memoria, del Motorola 68000.

Cicli sincroni

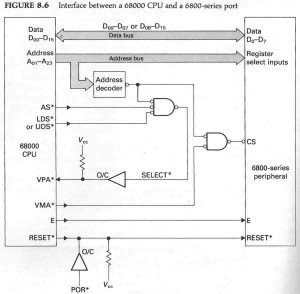

Fermo restando quanto già detto in relazione ai pins di controllo del bus sincrono introduciamo uno schema a blocchi dell'hardware necessario all'interfacciamento di periferiche sincrone con il Motorola 68000. (Figure 8.6)

Normalmente avremmo avuto il CS* della periferica direttamente connesso con la linea SELECT*.

In questo caso invece SELECT* è connessa con VPA* attraverso un buffer open collector di modo che quando la periferica sarà selezionata il 68000 verrà informato che il corrente ciclo di bus è sincrono.

DTACK* non prenderà parte alla temporizzazione del ciclo (come nel caso dei trasferimenti asincroni) e rimarrà quindi negato per tutto il tempo.

A questo punto, dopo l'asserzione di VPA*, la cpu porterà a livello logico basso VMA* nel corretto istante del ciclo di E. (La relazione temporale tra VMA* ed E è generata internamente al 68000).

VMA*, come si evince dalla figura, è in or con l'uscita della decodifica degli indirizzi.

CS* sarà dunque asserito quando VMA* sarà basso ed alla decodifica verrano forniti gli indirizzi corretti per la periferica.

Il ciclo, comune agli accessi di lettura e scrittura, terminerà con il fronte di discesa di E.

Riassumendo...

La figura 8.7 rappresenta il diagramma di flusso dei cicli sincroni del 68000 estrapolato dall'insostituibile Microprocessor systems Design di Alan Clements.

Thank you so much professor Clements!!!

Solo una piccola nota inerente il secondo passaggio (Request synchronous cycle) dove avrei ritenuto opportuno sottolineare come l'asserzione di VPA* sia più che altro frutto della logica esterna allo slave (come del resto si evince dalla Figura 8.6).

Cicli asincroni

Un ciclo asincrono, sia esso in lettura o scrittura, durerà in maniera indefinita fin quando la periferica a cui si accede (sia essa memoria od hardware di I/O) non restituirà un segnale di acknowledgement per informare il 68000 che sul bus sono finalmente presenti dati validi (lettura) o che i dati provenienti dalla cpu sono stati correttamente registrati (scrittura).

Questo permette al microprocessore di interfacciarsi con una serie di periferiche dai tempi di accesso assolutamente eterogenei.

Detto segnale di acknowledgement sara veicolato attraverso DTACK* ed ovviamente è generato dalla periferica a cui il 68000 intende accedere (o dalla logica di contorno che gestice suddetto device).

Fermo restando quanto si evince dalla figura 4.5 (si veda a tal riguardo la sezione dedicata al controllo del bus asincrono nella pagina dedicata alla piedinatura del Motorola MC68000) proviamo ad introdurre una nuova immagine rappresentante il diagramma temporale di un ciclo di lettura.

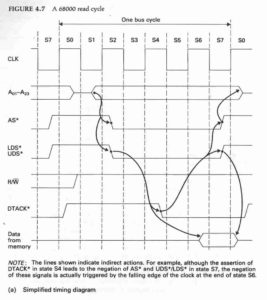

La figura 4.7 rappresenta un ciclo di lettura asincrono del Motorola MC68000.

Ogni accesso alla memoria (trasferimento dati verso il 68000) dura un minimo di 4 cicli di clock ed è diviso in 8 stati (S0 - S7).

Ogni ciclo inizia in S0 con il segnale di clock alto e termina in S7 con il clock basso.

Come anticipato poc'anzi il ciclo di lettura può essere esteso in maniera indefinita (i.e. fino alla asserzione di DTACK*) con l'inserimento di wait states tra gli stati S4 ed S5.

Ogni wait state ha la durata di mezzo ciclo di clock.

Analizziamo ora le varie fasi del ciclo scandite dagli 8 stati!

- S0: R/W è alto (lettura), tutti gli altri segnali sono negati.

- S1: Il bus indirizzi (A01-A23) presenta dati validi. Questa condizione non cambierà fino allo stato S0 del prossimo ciclo.

- S2: AS* viene asserito ad indicare che il contenuto del bus indirizzi è valido.

Va notato come non si possa dare per scontata la validità dei dati presenti sul bus indirizzi a partire dallo stato S1 in quanto questa caratteristica può variare in relazione alle differenti declinazioni della famiglia M68K.

Esclusivamente nei cicli di lettura, LDS* e/o UDS* vengono asseriti parallelamente ad AS*. E' questo il momento per far partire il circuito di gestione del DTACK*. - S3: In riferimento all' MC68000 ad 8Mhz in questo stato i segnali non subiscono modifiche. Nella versione di clock a 12.5Mhz AS* potrebbe essere negato proprio in S3.

- S4: Il ritardo tra l' asserzione dei data strobe (LDS*/UDS* che ricordiamo essere, in lettura,contemporaneo a quello di AS*) e l'asserzione di DTACK* deve consentirci di accedere correttamente alla memoria/periferica a cui stiamo riferendoci. (Vedi Data setup-time & data hold-time, introduzione ai diagrammi temporali).

Nel caso in cui DTACK* non venga asserito 20ns prima della fine di S4, degli wait states verranno inseriti tra S4 ed S5 fin quando DTACK* non sarà a livello logico zero. - S5: Fine di eventuali wait states.

- S6: Dati finalmente validi! (Ricordiamo che detta validità è affidata alla bontà della logica che gestisce il segnale di DTACK*. Inoltre stiamo assumendo non siano stati introdotti wait states.).

- S7: AS*, LDS* e/o UDS* vengono negati. I dati vengono finalmente acquisiti dal 68000. La memoria, grazie alla logica dedicata alla decodifica degli indirizzi, torna nello stato di alta impedenza.

DTACK* dovrà essere negato immediatamente dopo. (Vengono meno le condizioni di S2).

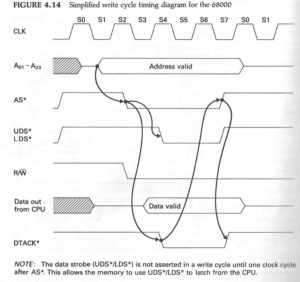

Diagramma temporale del ciclo di scrittura asincrono del Motorola MC68000.

Courtesy of Alan Clements

Per quanto riguarda invece il ciclo di scrittura lasciamo al lettore scoprire le differenze, poche, rispetto a quello di lettura.

Buon divertimento con le immagini qui a fianco! 🙂