MC68000 piedinatura

Iniziamo dalla piedinatura del 68000 e cerchiamo di raggrupparla in gruppi funzionali! Si faccia riferimento all'illustrazione a fianco.

Miscellaneous

Vcc e Gnd sono le linee di alimentazione.

La tensione richiesta è singola a +5V.

I pin sono duplicati per ridurre la caduta di tensione nei conduttori interni del chip.

BERR* è un pin di input attivo basso. (Questa categoria di pin verranno indicati con un asterisco).

E' utilizzato dalla logica esterna alla CPU per segnalare che qualcosa è andato storto nel ciclo di bus correntemente in eseguzione.

Nella mia realizzazione viene controllato da una sorta di watchdog che asserisce (porta a livello logico 0) il pin nel caso AS* non venga negato in un certo lasso di tempo.

Diversamente la CPU potrebbe attendere all'infinito l'asserzione di un DTACK* che potrebbe non arrivare mai.

(Si ricorda che AS* verrà negato dopo che la CPU ricevera il segnale di DTACK*)

Sarà tutto più chiaro parlando dei cicli di bus asincroni...

System control

CLK è il pin di input ad quale va fornito il segnale di clock a livello TTL.

Non si confonda il ciclo di clock con il ciclo di Bus che consiste di almeno 4 cicli di clock.

A sua volta l'esecuzione di una istruzione implica uno o più cicli di Bus.

RESET* è un pin bidirezionale attivo basso.

Abbiamo sentito migliaia di volte il suono di questa parola e migliaia di volte l'abbiamo utilizzata ma, nonostante questo, raramente abbiamo pensato ad una eventuale definizione da attribuirle.

In questo caso possiamo affermare che porre a livello logico basso questo segnale significhi mettere la CPU in uno stato conosciuto. Stop al caos dunque!

In questo caso RESET* lavora in coppia con HALT* ed all'atto dell'accensione devono essere asseriti entrambi per circa 100ms o più.

Passato questo lasso di tempo avremo la certezza che il registro A7 (puntatore allo stack) dello stato supervisore verrà caricato col contenuto dell'indirizzo zero della memoria ($00 0000).

Allo stesso modo il PC acquisirà il valore contenuto in $00 0004.

Questa linea può anche essere utilizzata come un output quando il 68000 esegue l'istruzione RESET.

In questo caso suddetto pin commuta allo stato logico 0 per 124 cicli di clock ponendo in stato di reset tutti i device connessi alla linea in questione.

Questa procedure non altera le operazioni interne della CPU. Il reset è valido solo per i device esterni.

HALT* pin bidirezionale attivo basso.

Qualora asserito provoca l'interruzione delle operazioni da parte del 68000 alla fine del ciclo di bus corrente.

I bus dati ed indirizzi vengono posti in alta impedenza, i segnali di controllo vengono negati ed i 3 pin FC0-FC2 (function codes) rimangono inalterati.

Questa caratteristica è molto utile nella fase di debug in quanto permette l'esecuzione di un singolo ciclo di bus alla volta.

Inoltre HALT* è utilizzato dalla CPU anche come output per segnalare un errore non recuperabile. In questo caso il 68000 asserisce la linea e si arresta.

Address Bus

A1 - A23 pins di output.

Tralasciando l'ovvia funzione di specificare gli indirizzi su cui avverranno le operazioni di lettura o scrittura, le prime 3 linee (A1, A2 ed A3) hanno la funzione ausiliaria di supporto agli interrupts vettorizzati.

Durante l'Interrupt acknowledge sequence su queste linee verrà piazzato il livello di interrupt che sta per essere processato (informazione utile per generare attraverso logica esterna al 68000 il corretto segale di IACK*).

Il bus indirizzi può essere messo in alta impedenza.

Data Bus

D0 - D15 pins bidirezionali.

Permette lo scambio di dati tra cpu e memorie/periferiche.

Anche il bus dati ha il suo ruolo specifico durante Interrupt acknowledge sequence in quanto la periferica richiedente identificherà se stessa ponendo l'interrupt vector number sulle linee D0 - D7.

Anche questo bus può essere posto in alta impedenza.

Asynchronous bus control

R/W* Pin di output che stabilisce se il corrente ciclo di accesso alla memoria è in scrittura (R/W= 0) od in lettura (R/W=1).

Durante lo svolgimento di operazioni interne il pin è sempre 1.

Può sembrare inutile sottolineare che questa linea debba essere a livello logico basso solo durante la scrittura.

Ne consegue che sia buona norma collegarla per mezzo di una resistenza di pull up a Vcc poiché, quando il 68000 mette in alta impedenza le linee di controllo, il comportamento di questa linea è indefinito e di certo non vorremmo trovarci nelle condizioni di effettuare scritture in memoria non pianificate.

AS* address strobe, pin di output attivo basso.

Quando asserito indica la validità dei dati sul bus indirizzi.

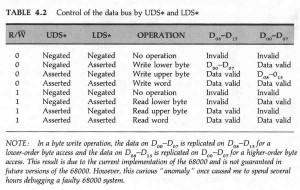

UDS* & LDS* upper & lower data strobe, pins di output che decidono l'ampiezza dell'accesso alla memoria.

Nel caso di una word sono entrambi asseriti.

Quando si effettua una lettura o scrittura ampia un byte è asserita la sola linea corrispondente (LDS* D0 -D7, UDS* D8 - D15).

E' interessante pensare a queste 2 linee come rimpiazzo della linea A0 del bus indirizzi.

Proviamo a riflettere un istante.. A0 sarebbe stato il bit meno significativo del bus, quindi da asserito avrebbe indirizzato una locazione dispari mentre da negato una locazione pari.

Possiamo ottenere lo stesso risultato con il lower data strobe che quando asserito ci permette di indirizzare una locazione dispari mentre l'upper data strobe ci permette di accedere a quella pari.

DTACK* data transfer acknowledge, pin di input attivo basso.

Questa è una delle linee che mi divertono di più! E' il cuore del controllo dei cicli di bus asincroni. Questo segnale deve essere generato dalla periferica a cui il 68000 vuole accedere.

Sta a significare che il dispositivo acceduto ha posto i dati richiesti sul bus e che la CPU può ritenerli validi e procedere. Quando il segnale è negato il 68000 semplicemente.... aspetta!

In questo caso il successivo ciclo di clock, chiamato wait state, verrà introdotto come lasso di tempo dopo il quale il segnale di Data Transfer Acknowledge sarà controllato nuovamente.

Questa situazione verrà sbloccata o con l'asserzione di DTACK* o con quella di BERR*.

La situazione ideale quindi è quella di avere una periferica veloce che fornisca il Data Transfer Acknowledge nel più breve tempo possibile.

Ancora meglio collegare il pin a gnd. Qualcuno di noi sta pensando a quella famosa newsletter della prima metà degli anni 80?? Il titolo era davvero azzeccato! DTACK Grounded.

Bus Arbitration Control

BR* bus request, input attivo basso.

BG* bus grant, output attivo basso.

BGACK* bus grant acknowledge, input attivo basso.

Queste linee sono utilizzate quando il 68000 cede la sua leadership di bus master a dispositivi esterni come ad esempio DMACs (direct memory access controllers).

Bus request è utilizzato dal dispositivo che vuole prendere il controllo del bus di sistema per informare la cpu.

Bus grant viene asserito dal 68000 in risposta alla richiesta di bus grant ed indica al richiedente che il bus sarà disponibile alla fine del corrente ciclo di bus.

Bus grant acknowledge viene inviato dal nuovo bus master alla cpu per informare che la transazione ha avuto luogo. Il 68k può prendersi un poco di meritato riposo.

Function Code

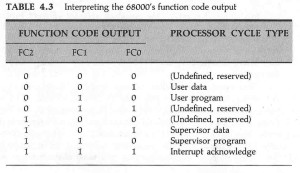

FC0 - FC2 function codes, output.

La decodifica di queste 3 linee ci permette di conoscere il tipo di ciclo correntemente in esecuzione.

Utili per ampliare la capacità di indirizzamento e per la connessione con una eventuale MMU.

Quando tutti ad 1 indicano che il 68000 sta servendo una richiesta di interrupt. Segnale che verrà sfruttato dal circuito di controllo degli interrupts.

Interrupt Control

IPL0* - IPL2*, input attivi bassi.

Le richieste di interrupt sono veicolate al 68000 attraverso queste linee con un codice a 3 bit che permette 7 livelli di interruzione.

0 indica che nessun interrupt è stato generato. I numeri salgono così come la priorità delle interruzioni fino al livello 7 che è sempre servito a prescindere dal settaggio della maschera di interrupt dello Status Register.

Synchronous Bus Control

Questa serie di pin permette il trasferimento di dati con periferiche di precedente generazione (6502, 6800, ecc) in momodalità sincrona.

VPA* valid peripheral address, input attivo basso è utilizzato dalla periferica per comunicare al 68000 che bisogna iniziare un trasferimento di dati sincrono.

VMA* valid memory address, output attivo basso è utilizzato dalla cpu per comunicare alla periferica che sul bus è ora presente un indirizzo valido.

E enable output, è un segnale di temporizzazione richiesto dalla periferica. E' asimmetrico e non in relazione di fase col clock del 68000. Il rapporto è di uno 1:10.

Un ciclo di E durerà quanto 10 cicli di clock della cpu. Asimmetrico in quanto sarà basso per 6 cicli di clock ed alto per 4.

Riassumendo...

Qui termina la disamina, seppur superficiale, della piedinatura del nostro amato MC68000.

Questo è un grosso passo avanti verso la comprensione di come realizzare un primitivo sistema in grado di emettere almeno un vagito.

Ritengo non sia difficile (farlo vagire intendo, educarlo sarà affar vostro!).

In bocca al lupo ed occhio alla tabella riassuntiva qui a fianco! 😉